Published on Nov 30, 2023

Before the 1950's, ferromagnetic cores were the only type of random-access, nonvolatile memories available. A core memory is a regular array of tiny magnetic cores that can be magnetized in one of two opposite directions, making it possible to store binary data in the form of a magnetic field. The success of the core memory was due to a simple architecture that resulted in a relatively dense array of cells.

This approach was emulated in the semiconductor memories of today (DRAM's, EEPROM's, and FRAM's). Ferromagnetic cores, however, were too bulky and expensive compared to the smaller, low-power semiconductor memories. In place of ferromagnetic cores ferroelectric memories are a good substitute. The term "ferroelectric' indicates the similarity, despite the lack of iron in the materials themselves.

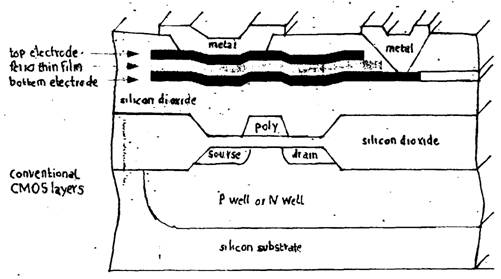

Ferroelectric memory exhibit short programming time, low power consumption and nonvolatile memory, making highly suitable for application like contact less smart card, digital cameras which demanding many memory write operations. In other word FRAM has the feature of both RAM and ROM. A ferroelectric memory technology consists of a complementary metal-oxide-semiconductor (CMOS) technology with added layers on top for ferroelectric capacitors. A ferroelectric memory cell has at least one ferroelectric capacitor to store the binary data, and one or two transistors that provide access to the capacitor or amplify its content for a read operation.

A ferroelectric capacitor is different from a regular capacitor in that it substitutes the dielectric with a ferroelectric material (lead zirconate titanate (PZT) is a common material used)-when an electric field is applied and the charges displace from their original position spontaneous polarization occurs and displacement becomes evident in the crystal structure of the material. Importantly, the displacement does not disappear in the absence of the electric field. Moreover, the direction of polarization can be reversed or reoriented by applying an appropriate electric field.

A hysteresis loop for a ferroelectric capacitor displays the total charge on the capacitor as a function of the applied voltage. It behaves similarly to that of a magnetic core, but for the sharp transitions around its coercive points, which implies that even a moderate voltage can disturb the state of the capacitor. One remedy for this would be to modify a ferroelectric memory cell including a transistor in series with the ferroelectric capacitor. Called an access transistor, it wo control the access to the capacitor and eliminate the need for a square like hysteresis loop compensating for the softness of the hysteresis loop characteristics and blocking unwanted disturb signals from neighboring memory cells.

Once a cell is accessed for a read operation, its data are presented in the form of an anal signal to a sense amplifier, where they are compared against a reference voltage to determine the logic level.

Ferroelectric memories have borrowed many circuit techniques (such as folded-bitline architecture) from DRAM's due to similarities of their cells and DRAM's maturity. Some architectures reviewed are,

" Wordline-parallel Plateline (WL//PL);

" Bitline-parallel Plateline (BL//PL);

" Segmented plateline (segmented PQ);

" Merged Wordline/Plateline architecture (ML);

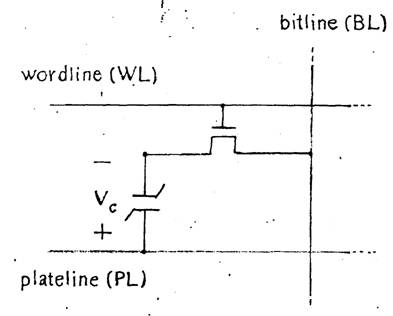

A ferroelectric memory cell, known as IT- IC (one transistor, one capacitor) ,structure which is similar to that of DRAM. The difference is that ferroelectric film is used as its storage capacitor rather than paraelectric material as in DRAM.

Figure above shows memory cell structure, consists of a single ferroelectric capacitor that is connected to a Plateline(PL) at one end and, via an access transistor, to a Bitline(BL) at the other end. Raising the wordline (WL) and hence turning ON the access transistor accesses the cell.

As shown in fig 2 ferroelectric memory technology consists of a CMOS technology with added layers on top for ferroelectric capacitors. Therefore, by masking parts of the design that are not using ferroelectric capacitors, CMOS digital and analog circuits can be integrated together with ferroelectric memories, all in the same chip. Ferroelectric capacitors to sit directly on the top of the transistors by means of stacked vias, hence reducing cell area.

The basic building block of FRAM is the Ferroelectric capacitor. A ferroelectric capacitor physically distinguished from a regular capacitor by substituting the dielectric with a ferroelectric material. In a regular dielectric, upon the application of an electric field, positive and negative charges will be displaced from their original positions-a concept that is characterized polarization. This polarization, or displacement, will vanish, however, when the electric field return back to zero. In, a ferroelectric material, on the other hand, there is a spontaneous polarization displacement that is inherent to the crystal structure of the material and does not disappear in the absence of electric field. The direction of this polarization can be reversed or reoriented by applying an appropriate electric field.

Widely used dielectric material is Lead Zirconate Titanate (PZT) with formula Pb(Zrx Ti1-x )03. Fig 3 illustrates a unit cell of this material. The central atom in this unit cell either Titanium (Ti) or Zirconium (Zi), depending on the contribution of each atom to the material formula. Lead (Pb) are at the corner of the cube and Oxygen (02) at the face center of the cub lattices

| Are you interested in this topic.Then mail to us immediately to get the full report.

email :- contactv2@gmail.com |